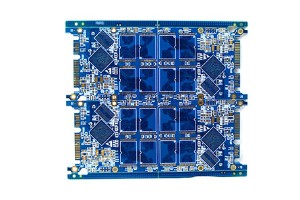

8 Layer ENIG FR4 Multilayer PCB

D'Schwieregkeet vu Multilayer PCB Board Prototyping

1. D'Schwieregkeet vun der Interlayer Ausrichtung

Wéinst de ville Schichten vun multilayer PCB Verwaltungsrot, ass d'Eechung Noutwendegkeete vun PCB Layer méi héich a méi héich.Typesch gëtt Ausriichtung Toleranz tëscht Schichten bei 75um kontrolléiert.Et ass méi schwéier d'Ausrichtung vu Multilayer PCB Board ze kontrolléieren wéinst der grousser Gréisst vun der Eenheet, der héijer Temperatur an der Fiichtegkeet am Grafikkonversiounsworkshop, d'Dislokatiounsiwwerlappung verursaacht duerch d'Inkonsistenz vu verschiddene Kärplaten, an de Positionéierungsmodus tëscht Schichten .

2. D'Schwieregkeet vun der banneschten Circuitproduktioun

D'Multilayer PCB Board adoptéiert speziell Materialien wéi héich TG, héich Geschwindegkeet, héich Frequenz, schwéier Kupfer, dënn dielektresch Schicht an sou weider, wat héich Ufuerderunge fir bannescht Circuitproduktioun a Grafikgréisstkontrolle stellt.Zum Beispill erhéicht d'Integritéit vun der Impedanzsignaliwwerdroung d'Schwieregkeet vun der Fabrikatioun vum banneschten Circuit.D'Breet an d'Linnabstand si kleng, den oppene Circuit a Kuerzschluss erhéijen, de Passrate ass niddereg;mat méi dënn Linn Signal Schichten, der bannenzegen AOI Auswee Detektioun Wahrscheinlechkeet vergréissert.Déi bannenzeg Kärplack ass dënn, einfach ze falen, schlecht Belaaschtung, einfach ze krullen Ätz;multilayer PCB ass meeschtens System Verwaltungsrot, déi méi grouss Eenheet Gréisst a méi Eiseschrott Käschten huet.

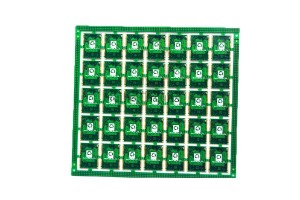

3. Schwieregkeeten an der Laminéierung an der passender Fabrikatioun

Vill banneschten Kär Brieder an semi-geheelt Brieder sinn iwwerlagert, déi ufälleg fir Mängel wéi Rutsch Plack, Laminatioun, resin ongëlteg a Bubble Reschter an STAMPING Produktioun sinn.Am Design vun kaschéierte Struktur soll d'Hëtzt Resistenz, Drock Resistenz, gekollt Inhalt an dielektresch deck vum Material voll considéréiert ginn, an eng raisonnabel Material pressen Schema vun multilayer Plack soll gemaach ginn.Wéinst der grousser Zuel vu Schichten sinn d'Expansioun an d'Kontraktiounskontroll an d'Gréisst Koeffizient Kompensatioun net konsequent, an déi dënn Inter-Layer Isoléierschicht ass einfach zum Echec vum Inter-Layer Zouverlässegkeetstest ze féieren.

4. Bueraarbechten Produktioun Schwieregkeeten

D'Benotzung vun héijer TG, héich Geschwindegkeet, héich Frequenz, décke Kupfer Spezialplack erhéicht d'Buerrauheet, d'Bohrung an d'Schwieregkeet fir d'Fleckentfernung ze bueren.Vill Schichten, Bueraarbechten sinn einfach ze briechen;CAF Echec verursaacht duerch dichte BGA a schmuel Lach Mauer Abstand ass einfach ze steig Buerproblem wéinst PCB deck ze féieren.