Duerch-Lach Design an héich Vitesse PCB

An héich Vitesse PCB Design, bréngt de scheinbar einfach Lach oft groussen negativen Effekt op de Circuit Design.Duerch-Lach (VIA) ass ee vun de wichtegste Komponente vunmultilayer PCB Conseils, an d'Käschte vun Bueraarbechten normalerweis Konte fir 30% ze 40% vun der PCB Verwaltungsrot Käschten.Einfach gesot, all Lach an engem PCB kann en Duerchgangsloch genannt ginn.

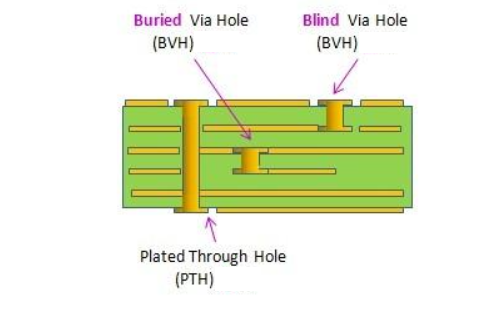

Aus der Siicht vun der Funktioun kënnen d'Lächer an zwou Zorte ënnerdeelt ginn: eng gëtt fir elektresch Verbindung tëscht Schichten benotzt, déi aner gëtt fir Apparatfixatioun oder Positionéierung benotzt.Wat den technologesche Prozess ugeet, sinn dës Lächer allgemeng an dräi Kategorien opgedeelt, nämlech blann via, cand duerch via.

Fir den negativen Impakt duerch de parasitären Effekt vun der Pore ze reduzéieren, kënnen déi folgend Aspekter sou wäit wéi méiglech am Design gemaach ginn:

Bedenkt d'Käschte an d'Signalqualitéit, gëtt e vernünftegt Gréisst Lach gewielt.Zum Beispill, fir 6-10 Layer Memory Modul PCB Design, ass et besser eng 10/20mil (Lach / Pad) Lach ze wielen.Fir e puer héich-Dicht kleng Gréisst Verwaltungsrot, Dir kënnt och probéieren 8/18mil Lach ze benotzen.Mat der aktueller Technologie ass et schwéier méi kleng Perforatiounen ze benotzen.Fir d'Energieversuergung oder Buedem Drot Lach kann considéréiert ginn eng méi grouss Gréisst ze benotzen, der impedance reduzéieren.

Vun den zwou Formelen uewe diskutéiert, kann et ofgeschloss ginn datt d'Benotzung vun engem méi dënnen PCB Board profitabel ass fir déi zwee parasitär Parameter vun der Pore ze reduzéieren.

D'Pins vun der Energieversuergung an dem Buedem sollen an der Géigend gebohrt ginn.Wat méi kuerz d'Leads tëscht de Pins an de Lächer sinn, wat besser ass, well se zu enger Erhéijung vun der Induktioun féieren.Zur selwechter Zäit sollten d'Energieversuergung an d'Buedemleit esou déck wéi méiglech sinn fir d'Impedanz ze reduzéieren.

D'Signal Wiring op derhéich-Vitesse PCB Verwaltungsrotsoll Schichten net sou vill wéi méiglech änneren, dat ass, fir onnéideg Lächer ze minimiséieren.

E puer Buedem Lächer ginn no bei de Lächer an der Signalaustauschschicht plazéiert fir eng enk Loop fir d'Signal ze bidden.Dir kënnt souguer vill extra Buedem Lächer op derPCB Verwaltungsrot.Natierlech musst Dir flexibel an Ärem Design sinn.Den Duerchschnëttsmodell hei uewen diskutéiert huet Pads an all Schicht.Heiansdo kënne mir Pads an e puer Schichten reduzéieren oder souguer ewechhuelen.

Besonnesch am Fall vun enger ganz grousser Pore Dicht kann et zu der Bildung vun enger gebrochener Groove an der Kupferschicht vum Trennschalter féieren.Fir dëst Problem ze léisen, zousätzlech fir d'Positioun vun der Pore ze beweegen, kënne mir och d'Reduktioun vun der Gréisst vum Lötpad an der Kupferschicht berücksichtegen.

Wéi iwwer Lächer ze benotzen: Duerch déi uewe genannte Analyse vun de parasitäre Charakteristiken vun iwwer Lächer kënne mir gesinn datt anhéich-Vitesse PCBDesign, déi scheinbar einfach falsch Notzung vun iwwer Lächer bréngt dacks grouss negativ Auswierkungen op de Circuitdesign.

Post Zäit: Aug-19-2022