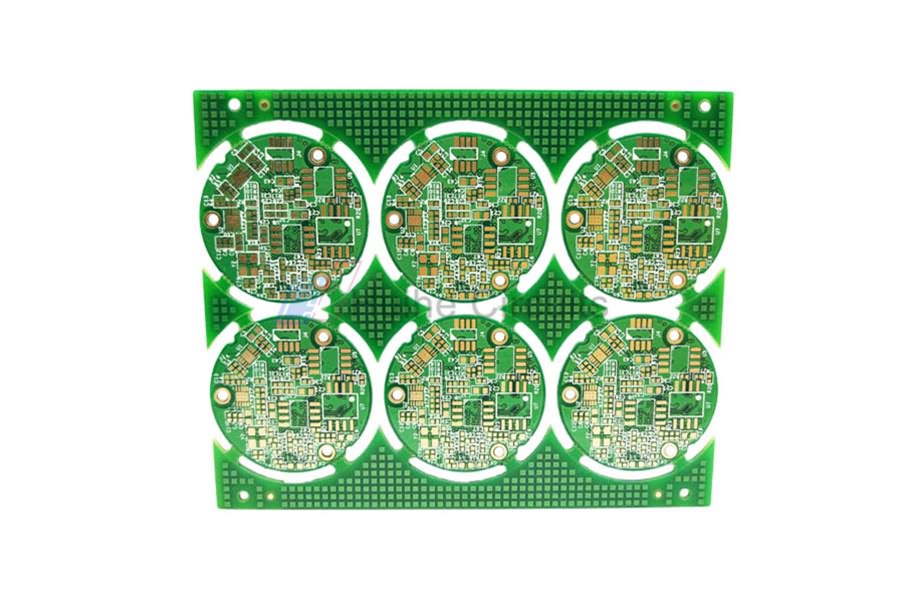

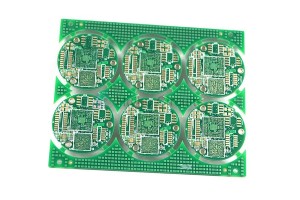

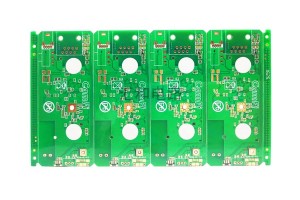

8 Layer ENIG FR4 Via-In-Pad PCB

Déi schwieregst Saach fir de Plug-Lach am Via-in-Pad ze kontrolléieren ass de Solderkugel oder Pad op der Tënt am Lach.Wéinst der Noutwennegkeet vun der Benotzung vun héijer Dicht BGA (Ball Grid Array) an der Miniaturiséierung vum SMD Chip, ass d'Applikatioun vun der Schacht Lach Technologie ëmmer méi.Duerch den zouverlässeg duerch Lach Füllprozess kann d'Plack Lach Technologie fir den Design an d'Fabrikatioun vun High-Density Multilayer Board applizéiert ginn, an anormal Schweess vermeiden.HUIHE Circuits benotzt via-in-Pad Technologie fir vill Joren, an huet en effizienten an zouverléissege Produktiounsprozess.

Parameter vun Via-In-Pad PCB

| Konventionell Produkter | Spezial Produkter | Spezial Produkter | |

| Lach Fëllung Standard | IPC 4761 Typ VII | IPC 4761 Typ VII | - |

| Min Hole Duerchmiesser | 200 µm | 150 µm | 100 µm |

| Minimum Pad Gréisst | 400 µm | 350 µm | 300 µm |

| Max Hole Duerchmiesser | 500 µm | 400 µm | - |

| Maximal Pad Gréisst | 700 µm | 600 µm | - |

| Minimum Pin Pitch | 600 µm | 550 µm | 500 µm |

| Aspektverhältnis: Konventionell via | 1:12 | 1:12 | 1:10 |

| Aspektverhältnis: Blann iwwer | 1: 1 | 1: 1 | 1: 1 |

Funktioun vun Plug Hole

1.Verhënnert datt d'Zinn duerch d'Leedungsloch duerch d'Komponentefläche wärend der Welleléisung passéiert

2.Avoid Flux Rescht am duerch-Lach

3.Prevent Zinn Kugelen aus Poppen eraus während Welle soldering, doraus zu kuerz Circuit

4.Verhënnert datt d'Uewerflächesolderpaste an d'Lach fléisst, wat virtuell Schweess verursaacht an d'Fitting beaflosst

Virdeeler vun Via-In-Pad PCB

1.Improve Hëtzt dissipation

2.D'Spannungsstand Kapazitéit vu Vias gëtt verbessert

3.Provide eng flaach a konsequent Uewerfläch

4.Lower parasitic inductance

Eise Virdeel

1. Eegent Fabréck, Fabréck Beräich 12000 Quadratmeter, Fabréck direkt Verkaf

2. D'Marketing-Team bitt séier a qualitativ héichwäerteg Pre-Sales an After-Sales Servicer

3.Process-baséiert Veraarbechtung vu PCB Designdaten fir sécherzestellen datt d'Clienten an der éischter Kéier iwwerpréiwen a bestätegen